芯片产品

热点资讯

- 关于电子元器件 TLV1117LV33DCYR 这颗芯片的参数PDF资料介绍

- 如何正确应用FPGA的四种时钟资源?

- Analog Devices ADG6412BCPZ-REEL7

- 关于电子元器件 TCM1-63AX+ 这颗芯片的参数PDF资料介绍

- 关于电子元器件 XQR5VFX130-1CN1752V 这颗芯片的参数PDF资料介绍

- 什么是磁通门原理?磁通门传感器优缺点

- 【器件篇】MEMS气体传感器基础知识详解

- 关于电子元器件 ULN2003D1013TR 这颗芯片的参数PDF资料介绍

- Xilinx XC2C512-7FT256C

- 关于电子元器件 TJA1043T 这颗芯片的参数PDF资料介绍

- 发布日期:2023-12-26 15:10 点击次数:81

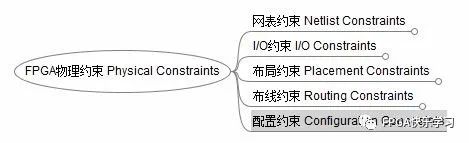

所谓配置约束,主要针对的是将工程所产生的二进制文件加载到FPGA器件相关的一些配置设置。

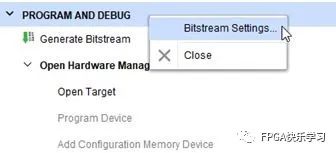

Xilinx Vivado工具的配置约束隐藏得比较深,如图1所示,在进入配置页面前,首先需要点击PROGRAM AND DEBUG->Generate Bitstream执行工程的全编译,然后点击IMPLEMENTATION->OpenImplemented Design进入实现页面。

图1Generate Bitstream菜单

接着如图2所示,在PROGRAMAND DEBUG上单击右键,在弹出的右键菜单中点击Bitstream Settings。

图2Bitstream Settings菜单

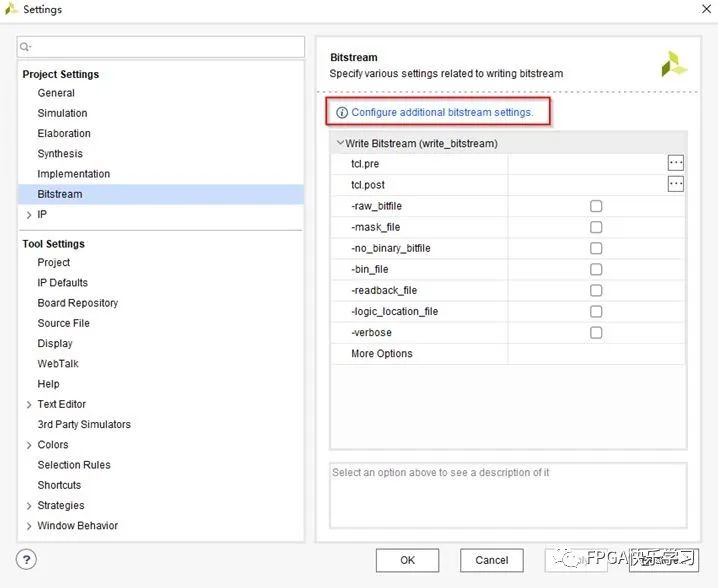

接着弹出如图3所示的BitstreamSettings页面,同时会出现Configure additional bitstream settings一行字符串(注意一定要按照前面的要求对工程进行全编译并点击Open Implemented Design进入实现页面才会出现该字符串),可以点击它。

图3Bitstream Settings页面

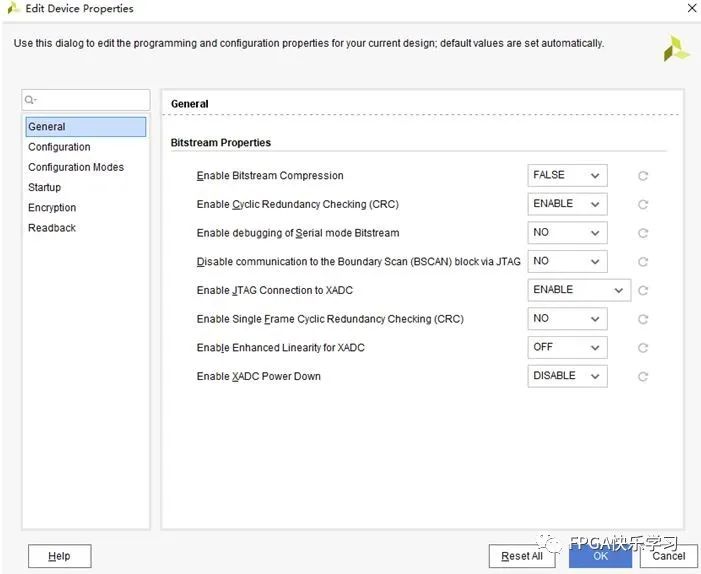

如图4所示,弹出的EditDevice Properties页面, CMOS图像传感器集成电路芯片这里的多个选项卡就是配置相关的所有详细约束。

图4 EditDevice Properties页面

下面列举几个比较常用的配置, EEPROM带电可擦可编程存储器芯片大全略作说明。

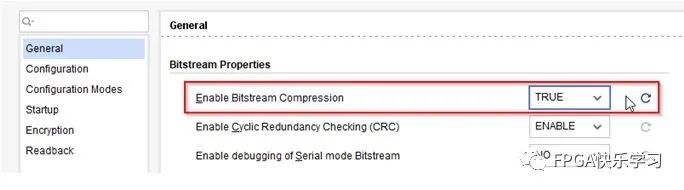

使能比特流压缩

如图5所示, 电子元器件PDF资料大全在General选项卡的EnableBitstream Compression后面,芯片交易网IC交易网默认的FALSE修改为TRUE, ATMEGA系列ATMEL芯片COM就使能了配置比特流的压缩功能。

图5 比特流压缩使能

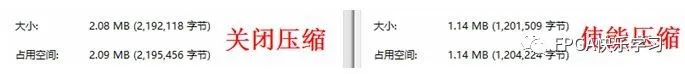

如图6所示,电子元器件PDF资料大全在本实例中,压缩前后的比特流数据量从2.08MB降低到了1.14MB,几乎压缩了一半的数据量,对于外部存储器容量受限的情况,该配置或许能够解燃眉之急。

图6 压缩前后数据量比对

SPI Flash加载配置

FPGA器件本身是基于RAM结构,每次启动必须有一颗外部的非易失存储器用于加载比特流。SPI Flash是最常用的用于加载FPGA的外部存储器,若希望生成用于存储到SPI Flash中的比特流,则需要先在配置选项中做一些设置。

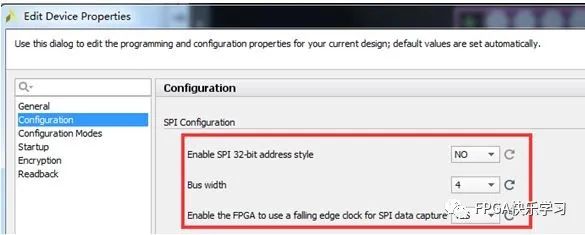

如图7所示,Configuration选项卡中的SPIConfiguration配置必须和实际使用的SPI Flash的参数相匹配。只有这里进行了正确配置后,生成的bit文件才能支持转换为用于SPI flash烧录固化的mcs格式文件。

图7 SPIFlash配置页面

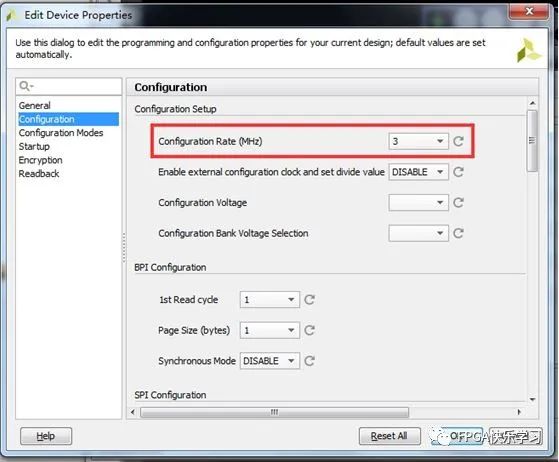

此外,如果希望调整SPIFlash加载FPGA过程的时钟频率,如图8所示,点击Configuration选项卡,修改第一行Configuration Rate (MHz)后的数值,即FPGA主动配置模式下CCLK的时钟频率。

图8配置时钟频率设定

审核编辑:黄飞

- 关于电子元器件 LPC1768FBD100 这颗芯片的参数PDF资料介绍2025-11-12

- 关于电子元器件 LPC1778FBD208 这颗芯片的参数PDF资料介绍2025-11-11

- 关于电子元器件 LPC2148FBD64 这颗芯片的参数PDF资料介绍2025-11-10

- 关于电子元器件 LPC2387FBD100 这颗芯片的参数PDF资料介绍2025-11-09

- 关于电子元器件 LS1020AXN7KQB 这颗芯片的参数PDF资料介绍2025-11-08

- 关于电子元器件 LSM6DS3TR-C 这颗芯片的参数PDF资料介绍2025-11-07